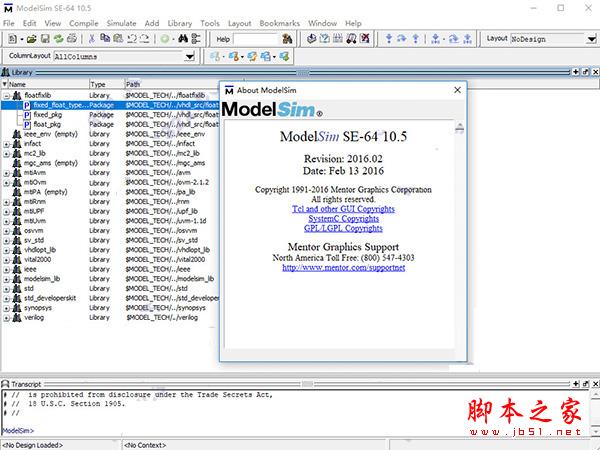

Modelsim SE是一款非常強大的HDL語言仿真軟件,它能提供友好的仿真環境,他有se、de、pe等多個版本,WinWin7下載為大家帶來的就是所有的版本功能最強速度最快的這款—Modelsim SE 10.5a,該版本全面支持VHDL和Verilog語言的IEEE 標準,支持C/C++功能調用和調試e-level)的代碼。這款語言仿真軟件采用直接優化的編譯技術、Tcl/Tk技術、和單一內核仿真技術。本文中winwin78給大家分享的Modelsim SE自帶破解補丁,下面給大家分享一下安裝與破解方法!

主要特點:

· RTL和門級優化,本地編譯結構,編譯仿真速度快,跨平臺跨版本仿真;

· 單內核VHDL和Verilog混合仿真;

· 源代碼模版和助手,項目管理;

· 集成了性能分析、波形比較、代碼覆蓋、數據流ChaseX、Signal Spy、虛擬對象Virtual Object、Memory窗口、Assertion窗口、源碼窗口顯示信號值、信號條件斷點等眾多調試功能;

· C和Tcl/Tk接口,C調試;

· 對SystemC的直接支持,和HDL任意混合;

· 支持SystemVerilog的設計功能;

· 對系統級描述語言的最全面支持,SystemVerilog,SystemC,PSL;

· ASIC Sign off。

· 可以單獨或同時進行行為(behavioral)、RTL級、和門級(gate-level)的代碼。

Modelsim SE安裝教程:

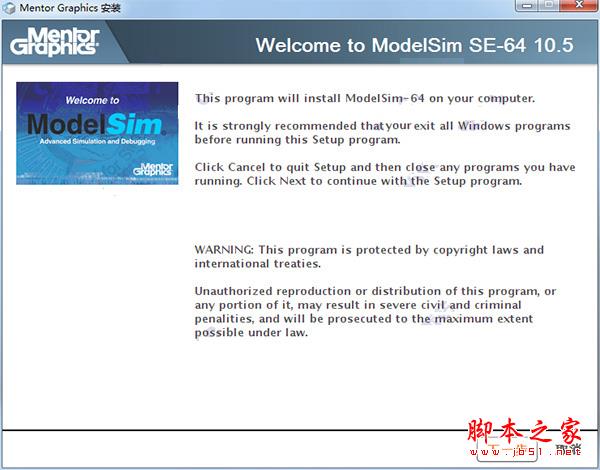

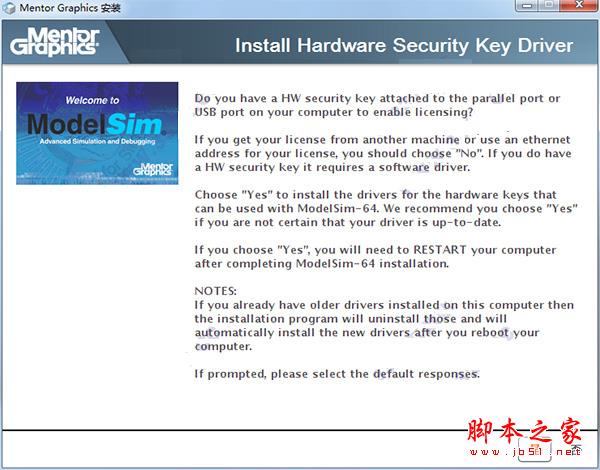

1、在本站下載并解壓,得到modelsim-win64-10.5-se.exe安裝程序和crak破解文件夾,雙擊主程序運行安裝,點擊下一步

modelsim-win32-10.1b-se.exe(版本可有不同)

MentorKG.exe(用于破解)

atch_dll.bat(用于破解)

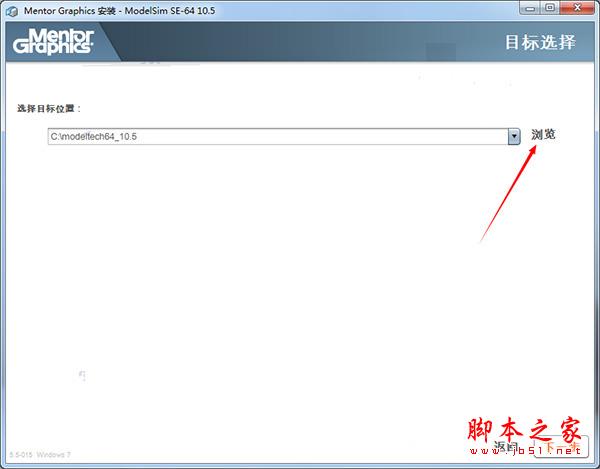

2、點擊瀏覽選擇安裝路徑,點擊下一步

3、點擊同意

4、正在安裝中,時間會比較長,耐心等待一會兒

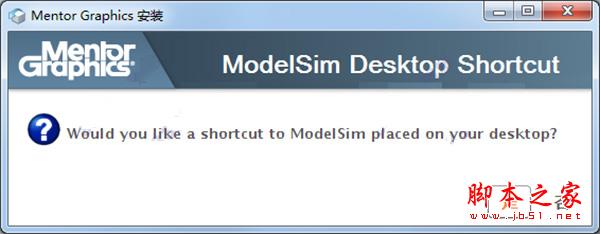

5、創建桌面快捷方式,點擊是

6、需要重啟計算機,點擊是

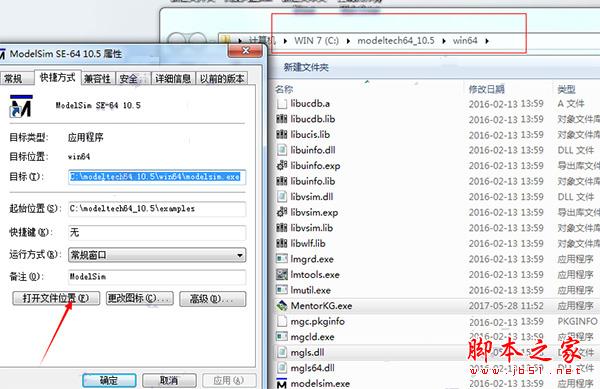

7、選中Modelsim SE 10.5,右鍵,雙擊打開軟件安裝位置,將crak破解文件夾中的MentorKG.exe、mgls.dll以及patch64_dll.bat復制到軟件安裝目錄下的Win64文件夾內

8、進入安裝目錄下的win64 文件夾找到mgls.dll mgls64.dll兩個文件,右鍵點擊屬性,去掉只讀屬性。

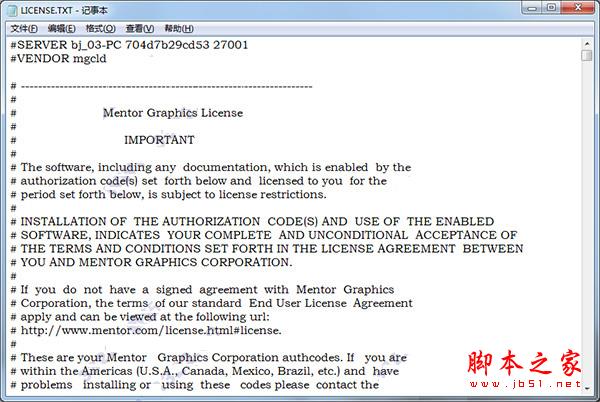

9、運行patch_dll.bat生成license文件后會自動用記事本打開license.txt.生成的license.txt,保存在安裝目錄中

10、右鍵點擊我的電腦,點擊屬性>高級系統設置>高級>環境變量>新建,新建用戶環境變量【MGLS_LICENSE_FILE】,變量值為license放置的目錄,例如:【C:\modeltech64_10.5\win64\LICENSE.TXT】,點擊確定即可破解成功

特色

1、統一的混合語言模擬引擎,易于使用和性能

2、Verilog的原生支持,用于設計的SystemVerilog,VHDL和SystemC,用于有效驗證復雜的設計環境

3、快速調試,易于使用,多語言調試環境

4、高級代碼覆蓋和分析工具,可實現快速覆蓋范圍

5、交互式和后期模擬調試可用,因此兩者都使用相同的調試環境

6、強大的波形比較,便于分析差異和錯誤

7、統一覆蓋數據庫,具有完整的交互式和HTML報告和處理功能,可以在整個項目中理解和調試覆蓋范

8、與HDL Designer和HDL Author相結合,可實現完整的設計創建,項目管理和可視化功能

功能

1、高級代碼覆蓋率

ModelSim的高級代碼覆蓋功能和易用性降低了利用這一寶貴驗證資源的障礙。

ModelSim高級代碼覆蓋功能為系統驗證提供了有價值的指標。 所有覆蓋信息都存儲在統一覆蓋數據庫(UCDB)中,該數據庫用于收集和管理高效數據庫中的所有覆蓋信息。 可以使用分析代碼覆蓋率數據的覆蓋率實用程序,例如合并和測試排名。 覆蓋結果可以交互式查看,模擬后或多次模擬運行合并后查看。 代碼覆蓋度量可以按實例或設計單位報告,從而提供管理覆蓋數據的靈活性。

支持的覆蓋類型包括:

聲明報道

運行期間執行的語句數

分行報道

影響HDL執行控制流的表達式和case語句

條件覆蓋

將分支上的條件分解為使結果為true或false的元素

表達范圍

與條件覆蓋相同,但涵蓋并發信號分配而不是分支決策

重點關注表達

以確定覆蓋結果的表達式的每個獨立輸入的方式呈現表達覆蓋率數據

增強的切換覆蓋范圍

在默認模式下,計數從低到高和從高到低的轉換;在擴展模式下,計算與X的轉換

有限狀態機覆蓋

州和州的過渡覆蓋范圍

2、混合HDL仿真

ModelSim將仿真性能和容量與模擬多個模塊和系統以及實現ASIC門級別簽核所需的代碼覆蓋和調試功能相結合。 全面支持Verilog,SystemVerilog for Design,VHDL和SystemC為單語言和多語言設計驗證環境提供了堅實的基礎。 ModelSim易于使用且統一的調試和仿真環境為當今的FPGA設計人員提供了他們不斷增長的高級功能以及使他們的工作高效的環境。

3、有效的調試環境

ModelSim調試環境為Verilog,VHDL和SystemC提供了廣泛的直觀功能,使其成為ASIC和FPGA設計的首選。

ModelSim通過智能設計的調試環境簡化了發現設計缺陷的過程。 ModelSim調試環境有效地顯示設計數據,以便分析和調試所有語言。

ModelSim允許在保存結果的仿真后以及實時仿真運行期間使用許多調試和分析功能。例如,coverage查看器使用代碼覆蓋率結果分析和注釋源代碼,包括FSM狀態和轉換,語句,表達式,分支和切換覆蓋率。

信號值可以在源窗口中注釋并在波形查看器中查看,從而簡化了對象及其聲明之間以及訪問文件之間的超鏈接導航的調試導航。

可以在列表和波形窗口中分析競爭條件,增量和事件活動。可以輕松定義用戶定義的枚舉值,以便更快地了解模擬結果。為了提高調試效率,ModelSim還具有圖形和文本數據流功能。

ModelSim與Mentor的旗艦模擬器Questa®共享一個共同的前端和用戶界面。這使客戶可以輕松升級到Questa,因為他們需要更高的性能并支持高級驗證功能。

Modelsim主要特點RTL和門級優化,本地編譯結構,編譯仿真速度快,跨平臺跨版本仿真;

單內核VHDL和Verilog混合仿真;

源代碼模版和助手,項目管理;

集成了性能分析、波形比較、代碼覆蓋、數據流ChaseX、Signal Spy、虛擬對象Virtual Object、Memory窗口、Assertion窗口、源碼窗口顯示信號值、信號條件斷點等眾多調試功能;

C和Tcl/Tk接口,C調試;

對SystemC的直接支持,和HDL任意混合;

支持SystemVerilog的設計功能;

對系統級描述語言的最全面支持,SystemVerilog,SystemC,PSL;

ASIC Sign off。

可以單獨或同時進行行為(behavioral)、RTL級、和門級(gate-level)的代碼。

上一篇:快優助手(自媒體運營工具)

360解壓縮軟件2023

360解壓縮軟件2023 看圖王2345下載|2345看圖王電腦版 v10.9官方免費版

看圖王2345下載|2345看圖王電腦版 v10.9官方免費版 WPS Office 2019免費辦公軟件

WPS Office 2019免費辦公軟件 QQ瀏覽器2023 v11.5綠色版精簡版(去廣告純凈版)

QQ瀏覽器2023 v11.5綠色版精簡版(去廣告純凈版) 下載酷我音樂盒2023

下載酷我音樂盒2023 酷狗音樂播放器|酷狗音樂下載安裝 V2023官方版

酷狗音樂播放器|酷狗音樂下載安裝 V2023官方版 360驅動大師離線版|360驅動大師網卡版官方下載 v2023

360驅動大師離線版|360驅動大師網卡版官方下載 v2023 【360極速瀏覽器】 360瀏覽器極速版(360急速瀏覽器) V2023正式版

【360極速瀏覽器】 360瀏覽器極速版(360急速瀏覽器) V2023正式版 【360瀏覽器】360安全瀏覽器下載 官方免費版2023 v14.1.1012.0

【360瀏覽器】360安全瀏覽器下載 官方免費版2023 v14.1.1012.0 【優酷下載】優酷播放器_優酷客戶端 2019官方最新版

【優酷下載】優酷播放器_優酷客戶端 2019官方最新版 騰訊視頻播放器2023官方版

騰訊視頻播放器2023官方版 【下載愛奇藝播放器】愛奇藝視頻播放器電腦版 2022官方版

【下載愛奇藝播放器】愛奇藝視頻播放器電腦版 2022官方版 2345加速瀏覽器(安全版) V10.27.0官方最新版

2345加速瀏覽器(安全版) V10.27.0官方最新版 【QQ電腦管家】騰訊電腦管家官方最新版 2024

【QQ電腦管家】騰訊電腦管家官方最新版 2024 360安全衛士下載【360衛士官方最新版】2023_v14.0

360安全衛士下載【360衛士官方最新版】2023_v14.0